## Santa Clara University

## **Scholar Commons**

## **Electrical and Computer Engineering**

School of Engineering

11-2020

# Carbon Nanotube-on-Graphene Heterostructures

Yu Zheng

Dongmeng Li

**Zubair Ahmed**

Jeongwon Park

Changjian Zhou

See next page for additional authors

Follow this and additional works at: https://scholarcommons.scu.edu/elec

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

Zheng, Y., Li, D., Ahmed, Z., Park, J., Zhou, C., & Yang, C. Y. (2020). Carbon Nanotube-on-Graphene Heterostructures. Journal of Electronic Materials, 49(11), 6806-6816. https://doi.org/10.1007/ s11664-020-08446-7

The final publication is available at Springer via https://doi.org/10.1007/s11664-020-08446-7.

This Article is brought to you for free and open access by the School of Engineering at Scholar Commons. It has been accepted for inclusion in Electrical and Computer Engineering by an authorized administrator of Scholar Commons. For more information, please contact rscroggin@scu.edu.

| Authors<br>Yu Zheng, Dongmeng Li, Zubair Ahmed, Jeongwon Park, Changjian Zhou, and Cary Y. Yang |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

## **Carbon Nanotube-on-Graphene Heterostructures**

Yu Zheng<sup>1\*</sup>, Dongmeng Li<sup>1</sup>, Zubair Ahmed<sup>2</sup>, Jeongwon Park<sup>3</sup>, Changjian Zhou<sup>4\*</sup>, and Cary Y. Yang<sup>1\*</sup>

<sup>1</sup>Center for Nanostructures, Santa Clara University

<sup>2</sup>Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology

<sup>3</sup>Department of Electrical & Biomedical Engineering, University of Nevada Reno

<sup>4</sup>School of Microelectronics, South China University of Technology

\*Corresponding authors

email addresses: \*yzheng1@scu.edu, dli2@scu.edu, zahmed@connect.ust.hk, jepark@unr.edu, \*zhoucj@scut.edu.cn, \*cyang@scu.edu

#### **Abstract**

A brief review of experimental and theoretical studies on a three-dimensional heterostructure consisting of vertical carbon nanotubes (CNTs) connected perpendicularly to a graphene layer is presented. This structure can serve as a potential building block for an all-carbon network in energy storage devices and on-chip interconnects. The review highlights reported works on the fabrication and characterization of such a heterostructure, with focus on the effect of the CNT-graphene interface on electrical conduction. While a direct comparison between experiment and theory is not possible at this time, a brief survey of theoretical efforts based on atomic cluster models nonetheless reveals important knowledge about the electronic transport properties of this all-carbon heterostructure.

Keywords: carbon nanotube, graphene, three-dimensional heterostructure, interface, all-carbon network, on-chip interconnect, energy storage device

#### 1. Introduction

Being the pre-eminent on-chip interconnect metal, copper (Cu) faces increased reliability challenges in the nanoscale. As the current density approaches or exceeds Cu's current-carrying capacity of  $J_{max} \sim 2 \times$  $10^6$  A cm<sup>-2</sup>, breakdown occurs due to electromigration [1-5]. Such  $J_{max}$  implies that a 50 nm  $\times$  50 nm Cu via can only sustain a current up to 50 µA, assuming that the current capacity does not degrade from its bulk value, which is unrealistic due to increased defect density in the nanoscale. Further, the resistivity of nanoscale Cu increases with decreasing linewidth due to enhanced surface and grain boundary scatterings [1]. Carbon nanomaterials such as graphene and carbon nanotube (CNT), on the other hand, possess currentcarrying capacities at least two orders of magnitude higher than that of Cu [6-9]. Thus, they have been proposed as materials for horizontal interconnects [10-12] as well as vertical vias [13-17]. Work on the characterization of graphene as a horizontal interconnect has been reported [10, 12], but the authors did not address how graphene would fit into an overall on-chip interconnect network. On the other hand, although studies have been carried out on CNT vias down to sub-100 nm dimensions [9, 16, 18], the resistance of the CNT vias is still much larger than those of Cu interconnects with similar dimensions. This large resistance is primarily due to the significant contact resistance between the CNTs and the metal underlayer [19-22]. Many efforts have been made to reduce the contact resistance for carbon-based electronic devices [23]. Both graphene and CNT have the same honeycomb structure, hence it is reasonable to envision a seamless contact between them [24]. A three-dimensional (3D) all-carbon structure consisting of vertical CNTs grown directly on horizontal graphene may conceivably serve as a building block in future on-chip interconnects [24-30]. In this review, we highlight some of the recent efforts in realizing this 3D CNTgraphene heterostructure, using well-known experimental and theoretical tools, their intended applications, and the challenges ahead.

In general, chemical vapor deposition (CVD) is the most common method for growing vertically aligned CNT directly on multilayer graphene [29, 31-38]. Several studies have been reported to synthesize seamless

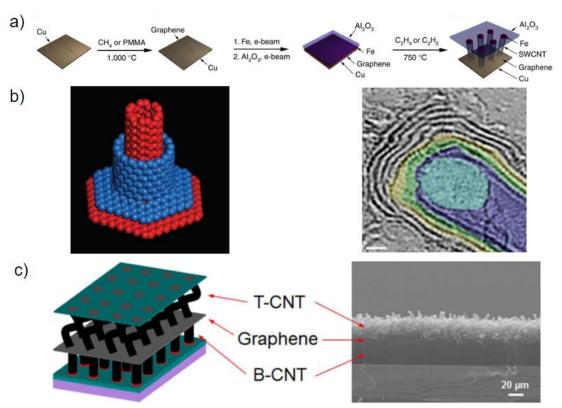

CNT-graphene vertical heterostructures, as illustrated in Figure 1. For example, Zhu [24] started with a CVD graphene-on-Cu substrate and coated it with a layer of iron (Fe) film using e-beam deposition. Then an alumina (Al<sub>2</sub>O<sub>3</sub>) film was deposited on the Fe catalyst film to serve as a floating buffer layer, as shown in Fig. 1(a). The floating buffer transformed the base growth of the CNTs into tip growth, thus allowing the CNTs to form an interface directly with graphene and achieving a seamless CNT-graphene heterostructure. High-resolution scanning transmission electron microscopy (STEM) image of the base of the CNT revealed an open-ended region surrounded by multiple walls of the CNT, as shown in Fig. 1(b). Therefore, the vertical CNT appeared to be a multi-walled CNT (MWCNT) that originated from a hole in the horizontal graphene layer. This CNT-graphene hybrid structure was envisioned as a high-performance supercapacitor device, due to its large surface area and ohmic conduction property [24]. Similarly, a CNT-graphene heterostructure was successfully synthesized on a porous nickel (Ni) foam by using the same method but with a better area utilization of the metal substrate [37]. Using the same approach as in Zhu [24], Jiang [39] succeeded in growing CNTs from both sides of graphene, as shown in Fig. 1(c). This unique structure has the potential to be used in energy storage that requires a high surface-to-volume ratio. As an alternative to using solid catalyst films, Salvatierra [40] spun a solution of Fe<sub>3</sub>O<sub>4</sub>/AlO<sub>x</sub> nanoparticles as the catalyst on the graphene/Cu substrate, and the method was also applicable to curved substrates. Being exposed to hydrogen at 750 °C, the catalyst nanoparticles became a mixture of Fe and Al<sub>2</sub>O<sub>3</sub>. Then a seamless CNTgraphene heterostructure was formed via tip growth mechanism, with the covalent C-C bonds at the CNTgraphene interface. By using Fe catalyst, single-walled CNTs (SWCNTs) can be grown at 950 °C on a FeMgAl layered double oxide substrate [41].

Figure 1: (a) Schematic for synthesis of CNTs directly from graphene [24]. (b) The image on the left is a proposed model of the CNT-graphene junction. The image on the right is a color-enhanced high-resolution bright-field STEM image of the base of a CNT. The cyan color represents the open-end region of the CNT, and the blue, green, and yellow colors represent the CNT walls [24]. (c) Schematic of a tip-growth T-CNT/graphene/base-growth B-CNT sandwich structure and the corresponding side-view SEM image of the structure. Between T-CNT and B-CNT is the few-layer graphene [39]. Figures (a) and (b) reprinted from Ref [24], Copyright 2012, with permission of Springer Nature. Figure (c) reprinted from Ref [39], Copyright 2016, with permission of American Chemical Society.

Compared to MWCNT, single-walled CNT (SWCNT) arrays have a higher surface-to-volume ratio and smaller defect density, while forming covalent C–C bonds at the CNT-graphene interface, leading to better electron transport [41]. Thus, SWCNT-graphene heterostructures seem suitable for applications as electrodes in high energy density batteries. In on-chip interconnects, the total resistance of a nanoscale Cu line on top of a Cu layer consists of three components, the line, the layer, and the interface between them. The latter is the dominant resistance component in the nanoscale, being inversely proportional to the contact diameter [22], as the electronic transport across the interface is quite different from that along the line and within the layer. If one can fabricate a CNT-graphene heterostructure such that the electronic transport across the interface is the same as that along the CNT and within graphene, the total resistance of the heterostructure could conceivably be comparable to its Cu counterpart.

It should be pointed out that all the vertical CNT-graphene heterostructures reviewed so far were synthesized with Fe as a catalyst. It is well-known that Fe is not compatible with silicon technology [42]. Therefore, to form a vertical CNT-graphene structure as a building block of on-chip interconnects, the use of Fe must be avoided. A suitable alternative is Ni, as described in the next section.

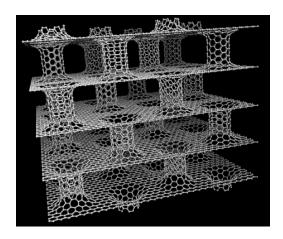

Parallel to experimental studies on synthesis and characterization, it is useful to examine the heterostructure using existing analytical tools with various degrees of rigor, by using suitable atomic clusters around the CNT-graphene interface, as reported previously [43, 44]. Figure 2 illustrates how CNTs and graphene can be joined to form a seamless vertical CNT-graphene heterostructure. In this multi-layered all-carbon structure, graphene serves as the platform for CNT growth, and the grown CNTs serve as pillars to support adjacent graphene layers [45].

In a seamless vertical CNT-graphene heterostructure, the region of interest is the interface between the vertical CNT and the horizontal graphene, where the carbon atoms at one end of the CNT are connected to the carbon atoms at the periphery of a hole formed in the graphene. Ideally, this C-C bonding is a covalent, sigma-type bond. The result would be a robust connection between the vertical CNT and the horizontal graphene. In such a scenario, all carbon atoms at the CNT-graphene interface would have sp²-hybridized bonding. Thus, each interfacial carbon atom forms three strong sigma-bonds with its three nearest neighbor atoms, respectively, leaving one p-orbital electron to form a pi-bond with its nearest neighbors. While such bonding at the interface is not planar, these relatively delocalized pi-electrons can preserve the in-plane electrical conduction across the interface between the CNT and the graphene. Since the seamless interface between CNT and graphene can yield a robust mechanical structure due to the strong sigma bonds and in-plane electrical conduction similar to that in graphene, the 3D CNT-graphene heterostructure would be an ideal candidate for end-of-roadmap generations of on-chip interconnects [46]. In this paper, we will review some of the recent efforts to meet this objective.

Fig. 2 Pillared graphene. Schematic of a 3D all-carbon CNT-graphene heterostructure [45]. Reprinted from Ref [45], Copyright 2008, with permission of American Chemical Society.

#### 2. Synthesis and characterization of CNT-graphene heterostructures

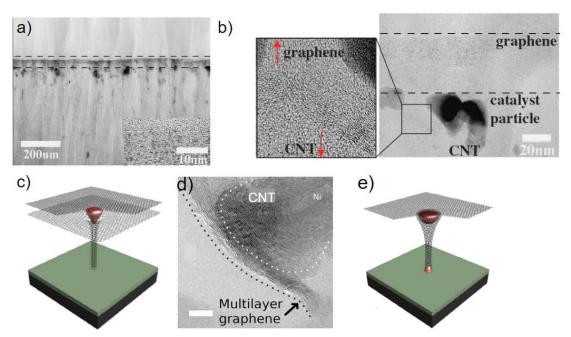

To synthesize a CNT-graphene heterostructure as a potential building block for on-chip interconnects, a CVD method using a two-step process is often used. First, graphene is grown on a metal substrate and subsequently transferred onto a target substrate. Second, the vertical CNT-graphene heterostructure is synthesized after catalyst deposition and introduction of a carbon source gas. The catalyst film thickness needs to be between 1 and 10 nm or thinner to yield good-quality CNTs. When the catalyst film thickness is increased further, graphene can also be formed. Therefore, CNT and graphene can be grown simultaneously to form a heterostructure if the thickness of the catalyst can be controlled within a few nanometers. Instead of the two-step growth method, a one-step method is also feasible for forming vertical CNT-graphene heterostructures, thus simplifying the growth process. In a reported process, a cobalt (Co) or Ni catalyst film was deposited onto a layer of TiN [47, 48]. The thickness of the catalyst film was a few nanometers so that both graphene and CNTs could be synthesized using the same catalyst. Graphene films were formed first, then the catalyst film dewetted to form nanoparticles. This film dewetting process was followed by CNT growth in tip-growth mode at a relatively low temperature (around 400 to 510 °C), resulting in a vertical CNT-graphene heterostructure on a silica substrate. This lower temperature ensures compatibility with the chip manufacturing process for the vertical CNT-graphene heterostructure to serve as part of an on-chip interconnect network. Depending on the catalyst type and condition, the CNTgraphene interface may have different configurations. Figs. 3(a) and 3(b) are cross-sectional TEM images of a CNT-graphene heterostructure formed using a 3.6 nm Co catalyst film deposited on a 5 nm TiN film [47]. The Co catalyst nanoparticle was found to be at the CNT-graphene interface. The vertical CNT appeared to originate from a hole in the horizontal graphene layer, forming a trumpet-like structure, which is schematically shown in Fig. 3(c). In contrast, Fig. 3(d) is a cross-sectional TEM image of another CNTgraphene interface, this time formed using a 6 nm Ni catalyst film deposited on a 10 nm TiN film [48]. Again, the catalyst nanoparticle was at the CNT tip. However, unlike the CNT-graphene structure depicted in Figs. 3(a)-(c), the CNT tip was wrapped around by a few graphene layers (FGLs), as schematically shown in Fig. 3(e). The shape of this closed CNT-graphene interface is similar to that observed at CNT-metal interface [21], and can result in higher electrical contact resistance than that for a configuration where the CNT gradually transforms into a flat graphene sheet. The fact that the CNT was closed by a number of graphene layers suggests that the CNTs grew from the base and not from the tip, as the base growth stopped when the catalyst was completely encapsulated by the CNT walls [48]. It is worth pointing out that in either case shown in Fig. 3, the catalyst nanoparticle was present at the CNT-graphene interface. However, the electrical conduction of this CNT-graphene heterostructure was not reported.

Fig. 3 (a) Cross-sectional TEM images of CNT-graphene heterostructures [47]. Multi-layer graphene was formed on top of the CNT bundle between the two parallel dashed lines and shown in the inset, estimated to be 30 nm and 105 layers. (b) TEM image around the connection between the graphene and a CNT [47]. Co catalyst nanoparticle was at the CNT-graphene interface. (c) Schematic of a CNT-graphene interface corresponding to the images in (b) [48]. (d) High-resolution TEM image of a CNT/FGLs interface [48]. The dotted lines denote the nanotube tip and the FGLs. The scale bar is 5 nm. The CNT was wrapped around by the FGLs. Ni nanoparticle was enclosed at the CNT tip. (e) Schematic of the CNT-graphene interface corresponding to the images in (d). The CNT grew from a catalyst particle at its base [48]. Figures (a) and (b) reprinted from Ref [47], Copyright 2008, with permission of The Japan Society of Applied Physics. Figures (c), (d), and (e) reprinted from Ref [48], Copyright 2011, with permission of AIP publishing.

Another one-step growth process used FeMoMgAl-layered double hydroxides as a catalyst to form a nitrogen-doped graphene-SWCNT hybrid (NGSH), which may be applied as a bifunctional electrocatalyst for both oxygen reduction reaction and oxygen evolution reaction in renewable energy devices such as fuel cells and metal-air batteries [49]. Similar to the results shown in Fig. 3, the catalyst nanoparticle resided at the CNT-graphene interface. After removal of the nanoparticle, the NGSH was available to be used as an oxygen electrode catalyst. Yet another one-step method has been reported to form a seamless graphene-CNT junction for energy conversion and storage application [50]. First, an aluminum wire was exposed to 0.3M oxalic acid solution at 40 V and 3 °C so that its external surface could be turned into anodized aluminum oxide. Then without additional metal nanoparticle catalyst and using CVD, a seamless CNT-graphene heterostructure was formed where radially aligned CNT arrays were surrounded by a cylindrical graphene layer, with covalently bonded seamless pure C-C nodal junctions between the graphene and the CNTs. After removing the aluminum and aluminum oxide with 1M KOH solution, a hollow 3D graphene-CNT fiber was obtained.

In general, the key in the one-step growth is the proper choice of catalyst (material and thickness) and temperature to form the two constituent nanocarbon materials sequentially or simultaneously. It should be noted that although the one-step method is capable of forming a CNT-graphene heterostructure without first growing and transferring graphene, the catalyst nanoparticle is always present at the CNT-graphene interface after growth. The nanoparticle may be removed by a chemical solvent to obtain a pristine CNT-graphene heterostructure to be used as an electrode in an energy storage device. However, this method does not appear to be compatible with the chip manufacturing process to form a seamless CNT-graphene interconnect without any catalyst nanoparticles present at the CNT-graphene interface.

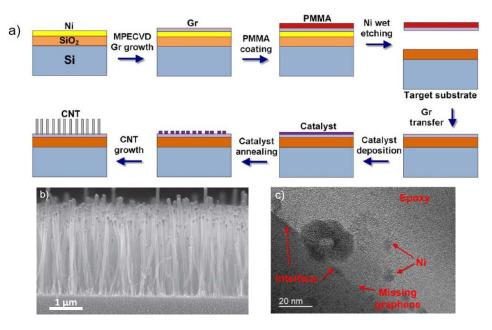

Fig. 4(a) illustrates a two-step fabrication process flow to form a CNT-graphene test structure, with potential application for on-chip interconnects [51]. The first step was the formation of graphene and its transfer onto a substrate. Fast microwave plasma-enhanced chemical vapor deposition (MPECVD) was used to grow graphene with evaporated 300 nm thick Ni catalyst film on a silicon substrate. The sample was first annealed at 900 °C in a H<sub>2</sub> atmosphere to increase the grain size of the Ni film and the uniformity of the graphene layer. This was followed by applying 200W microwave power to ignite the plasma. Graphene growth was then initiated by introducing CH<sub>4</sub> as a carbon source. After 10 s, the CH<sub>4</sub> gas flow was shut off and both the heater and plasma power were turned off to cool the substrate to room temperature in the H<sub>2</sub> ambient. After graphene growth, a 150 nm layer of PMMA was spin-coated on the graphene, which was then baked at 110 °C for 30 min to provide robust support in the subsequent releasing process. To enable graphene transfer onto other insulating substrates for further electrical characterization and CNT growth, the PMMA coated sample was put in a diluted HNO3 solution. The Ni catalyst film underneath the graphene was etched away by HNO<sub>3</sub>, thereby releasing the PMMA-graphene film. The PMMA-graphene film was then transferred onto the target substrate and put on a hotplate. Any trapped water at the graphenesubstrate interface was removed by slowly increasing the temperature of the hotplate to 90 °C. Then the PMMA was removed by rinsing the sample in acetone several times at 60 °C. After graphene formation and transfer, CNTs were then grown directly on graphene to produce a 3D heterostructure. A thin (~1-2 nm) layer of Ni catalyst was deposited on the graphene by e-beam evaporation. Upon annealing, the Ni catalyst film dewetted to form nanoparticles. The CNTs were then grown using a DC PECVD apparatus with C<sub>2</sub>H<sub>2</sub> as the carbon source. A vertical DC electric field perpendicular to the substrate was applied in the apparatus, igniting the plasma during CNT growth, and causing the CNTs to align vertically as they grew. This was a tip-growth process where the Ni catalyst particle stayed on top of the CNT as it grew from the graphene sheet. Thus, the resulting CNT-graphene heterostructure did not have the Ni nanoparticle at the CNT-graphene interface. The CNT-graphene heterostructure thus obtained was then analyzed with scanning electron microscopy (SEM) and transmission electron microscopy (TEM), and its electrical resistance was measured.

Fig. 4 (a) Two-step process flow of CNT-graphene heterostructure, consisting of (1) graphene growth on a substrate and graphene transfer on to a non-conductive substrate, and (2) CNT grown on the transferred graphene [51]. (b) Cross-sectional SEM image of CNT grown on graphene using Ni catalyst film (~1 nm) [51]. (c) Cross-sectional TEM images of the resulting CNT-graphene heterostructure. Some graphene layers are missing where CNT growth takes place, attributed to possible etching of graphene by Ni [51], and/or damage caused by plasma during CNT growth. Reprinted from Ref [51], Copyright 2017, with permission of IOP Publishing Ltd.

The SEM image shown in Fig. 4(b) suggests that the graphene layer under the vertically aligned CNTs was preserved after CNT growth [51]. Fig. 4(c) shows a cross-sectional TEM image of the CNT-graphene interface in the heterostructure. While graphene appeared to be present in parts of the interface, in other regions (especially where CNT growth took place), some graphene layers were missing. This was attributed to the etching of graphene by Ni, in which graphene dissolved in Ni and was used as a carbon source for CNT growth [51]. However, a more likely scenario is that the damage to graphene was caused by the plasma during CNT growth, as discussed below.

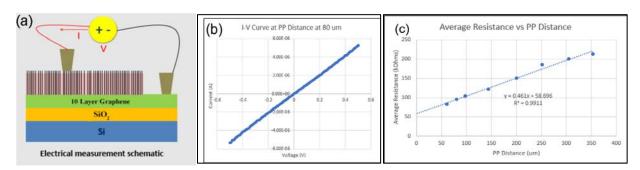

Electrical characteristics of the CNT-graphene heterostructure have been performed using a two-point current-voltage (I-V) measurement. Fig. 5 (a) shows the measurement schematic for a CNT-graphene test structure, grown with Ni catalyst using the PECVD process shown in Fig. 4(a) [52]. A key parameter for this PECVD process is the strength of the electrical field that must be applied to vertically align the CNTs during growth. It has been found if the field was too weak (for example, 500 V), the CNTs did not align well vertically. If the field was too strong (for example, 800 V), the CNT alignment was good, but the graphene underlayer suffered damage. To achieve good CNT alignment while preserving the underlying graphene, a lower DC voltage was applied. Fig. 5(b) shows a typical I-V behavior for a 600 VDC CNTgraphene heterostructure, where the two probes were placed 80 µm apart. The I-V relationship is linear, suggesting ohmic transport across the probe-CNT, probe-graphene, and CNT-graphene interface. Fig. 5(c) shows an average resistance of the heterostructure as a function of the probe-to-probe distance [53]. The linearly fitted line's vertical intercept provides a rough estimate of the contact resistance at the CNTgraphene interface (neglecting the resistance of the CNT array under the positive probe), which is around 50 k $\Omega$ . The slope can be used to extract the resistivity of the graphene layer of the test structure. This graphene resistivity was estimated to be around  $3.5 \times 10^{-4} \,\Omega \cdot \text{cm}$ , which was significantly higher than that of the ideal value of  $10^{-6} \Omega$  cm. We attribute this high graphene resistivity to be partly due to the damage to the graphene underlayer by the plasma during the PECVD process. Overall, the electrical characterization results indicate that the CNT-graphene heterostructure exhibits electrical conduction paths, despite damage to the graphene underlayer by the plasma during the PECVD process. If an optimum electric field value can be obtained to preserve the graphene underlayer while yielding vertically aligned CNTs, carrier transport through the CNT-graphene heterostructure can conceivably yield a much lower overall resistance. Work is currently in progress to achieve this objective.

Fig. 5 (a) Measurement schematic for CNT/multilayer graphene (MLG) test structure [52]. (b) Typical I-V behavior for 600 VDC PECVD CNT/MLG. (c) Average resistance vs PP distance for 600 VDC PECVD CNT/MLG sample. Plain MLG resistance is ~10 k $\Omega$  at a PP distance of 400  $\mu$ m [53]. Extracted resistivity of MLG in test structure is ~3.5×10<sup>-4</sup>  $\Omega$ ·cm, significantly higher than that of graphene ~10<sup>-6</sup>  $\Omega$ ·cm, due to some damage to MLG by plasma.

## 3. Theoretical studies of seamless CNT-graphene heterostructures

Although syntheses and characterizations of CNT-graphene heterostructures have been reported by many researchers in this field, there is still little evidence that these heterostructures possess a truly seamless connection [47, 48, 51]. Theoretical studies have been performed to study CNT-graphene heterostructures,

with the goal of simulating functional seamless structures and understanding their transport properties [33, 43, 44, 54, 55]. Numerous geometrical configurations for CNT-graphene heterostructures are possible due to the various CNT chiralities, the number of walls in a CNT, and the bonding type between CNT and graphene. Those that have been studied are constrained in part by the computational resources and the difficulty in establishing a stable junction between CNT and graphene. Interesting properties have been revealed by various theoretical studies [33, 54], though most remain unverified by experiment.

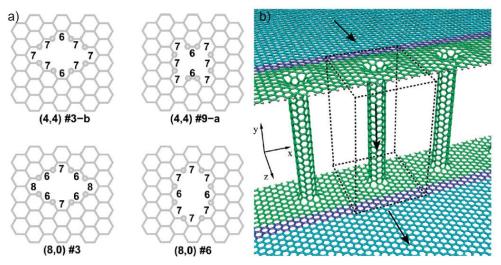

To form a seamless CNT-graphene heterostructure, a least-square method was utilized to achieve C–C bond lengths or bond-angles as close as possible to those of the ideal case [56, 57]. Moreover, Euler's theorem was applied to select the polygons for the CNT-graphene contact stitching process [56-60]. Fig. 6(a) shows the possible connections that the eight open bonds of a metallic (4,4) CNT or a semiconducting (8,0) CNT can form with the underlying graphene sheet [56]. Many theoretical calculations have adopted the same rules to form seamless CNT-graphene heterostructures [46, 61]. After identifying the bond contact spots on the graphene surface and the CNT, molecular dynamic simulations were performed to minimize the total binding energy of the heterostructure. With the optimized heterostructure, one can perform first-principles calculations to obtain electronic properties such as band structure, transmission coefficient, density of states (DOS), and conductance.

A first-principles calculation was performed by Novaes [44] to study the electronic transport properties of the (4,4) and (8,0) CNT-graphene heterostructures. For the metallic (4,4) CNT-graphene, two kinds of symmetrical connections containing six heptagonal rings at the interface (No. 3-b and No. 9-a in Fig 6(a)) were adopted. The unit cell of the periodic 3D seamless heterostructure shown in Fig. 6(b) was constructed for electronic transport simulation using the non-equilibrium Green's function (NEGF) method, and the current flow was through the CNT-graphene junction and the CNT itself. The conductance obtained from the simulation showed a weak dependence on CNT length for metallic CNTs. On the other hand, the conductance showed a strong dependence on the contact structure, with the No. 9-a contact structure exhibiting a higher conductance than the No. 3-b case. In contrast, the conductance of the semiconducting (8,0) CNT-graphene heterostructure showed a strong dependence on the CNT length and a weak dependence on the contact structure. Although the theoretical study reveals some interesting electronic transport properties of the CNT-graphene heterostructure, their calculations cannot ascertain the exact contribution of the CNT-graphene junction to the total conductance.

Fig. 6: (a) Scheme of the connection of graphene with the (4,4) and (8,0) CNTs for the different structures considered [44]. The small circles show the carbon atoms from graphene that bind to the atoms of the nanotube edge (not shown). The numbers indicate the sizes of the rings that result at each site upon the nanotube attachment. (b) Setup used for the transport calculations: an array of nanotubes connecting two semi-infinite graphene sheets [44]. The dotted lines enclose the atoms explicitly considered in the simulation box, which is repeated periodically in the x direction. Reprinted from Ref [44], Copyright 2010, with permission of American Chemical Society.

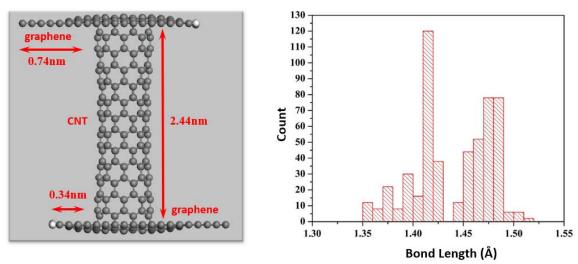

To better understand the CNT-graphene contact properties, the NEGF method was applied to a two-point graphene-CNT-graphene heterostructure [43]. Fig. 7(a) shows a schematic of the graphene-CNT-graphene heterostructure, which contained an (8,0) CNT with a radius of 0.626 nm and a length of 2.44 nm. Fig. 7(b) is a histogram depicting the distribution of C-C bond lengths of this structure. As expected, the most abundant bond length was 1.42 Å from the C-C bond in the graphene. The CNT contained many C-C bonds that were longer than 1.42 Å, as rolling up a graphene sheet into a CNT may lead to C-C bond elongation [62]. There were also a few C-C bonds of varying lengths, due to the presence of heptagonal and/or octagonal rings at the CNT-graphene interface (see Fig. 6(a)), as well as distorted C-C bonds in the CNT near the interface. The resistance of a graphene sheet for different lengths was calculated, which turned out to be 6.45 k $\Omega$  and independent of length, confirming ballistic transport. This result also served as a validation of the calculation method. The total resistance was found to be 91.5 k $\Omega$  for the heterostructure, with ohmic conduction across the CNT-graphene junction and possibly along the CNT as well. Furthermore, this result verified the previous study that semiconducting CNTs when contacted with graphene led to metallic behavior [54].

Work is in progress to go beyond this simple model used to study the interface between CNT and graphene, in order to better understand the transport within the heterostructure. For example, if the formation of a hole in the graphene does in fact take place to make room for a seamless interface with CNT, it would be worthwhile to study the effect of a second graphene layer below the surface. It is possible that this second layer, though weakly bonded to the top layer via van der Waals forces, serves to preserve the planarity of the top layer during the CNT growth. The planar top layer may in turn facilitate the covalent C-C bond formation across the interface.

Fig. 7 (a) Model of graphene-CNT-graphene heterostructure used for first-principles calculations and (b) a histogram showing the resulting bond lengths distribution.

#### 4. Potential applications of CNT-graphene heterostructures

Hydrogen has become an increasingly popular alternative energy source, but its storage in metal alloy tanks is inefficient. A vertical CNT-graphene heterostructure offers an alternative to store hydrogen, as its pore size and surface area can be increased by adjusting the CNT-graphene growth process parameters. A theoretical study was conducted and showed that this structure can be effective in increasing storage capacity [45]. Successful fabrication of the stacked CNT-graphene heterostructure can lead to a high-capacity hydrogen storage device in the future.

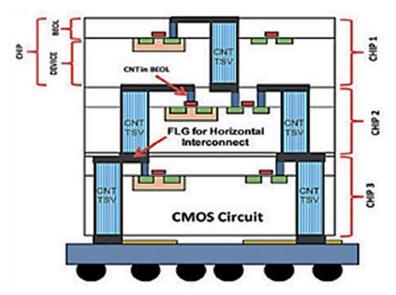

Continuous downward scaling in chip manufacturing has become a major challenge for on-chip interconnects. Due to electromigration challenges, on-chip Cu interconnect linewidth can no longer be reduced further in current technology nodes. Because of their high current capacity and superior transport properties, graphene [6, 11] and CNTs [16] have become potential candidates to replace Cu interconnects. However, the contact resistance between CNTs and conventional interconnect metal is a major challenge in functionalizing CNT vias [16]. Therefore, an all-carbon interconnect network consisting of vertical CNTs formed on horizontal graphene could mitigate the contact resistance challenge. Although the contact between CNTs and graphene can be refined to yield low resistance and variability, the contact resistivity can only be low as ~10<sup>-5</sup>  $\Omega$ ·cm² [25], which is still high for interconnect applications. Further, to facilitate the proper chip operation, CNTs must be grown on graphene at temperatures compatible to chip manufacturing, such as 550 °C [26], 510 °C [48] and 400 °C [47]. A schematic diagram for using CNTs and graphene as interconnects is shown in Fig. 8. Electrical characterization studies suggest that a conduction path does exist in 3D CNT-graphene test structures [51-53]. However, contact resistance remains a critical challenge in its implementation [51].

Fig. 8 Vertical CNT-graphene heterostructures as interconnects in CMOS circuit [26], showing few-layer graphene (FLG) that serves as horizontal interconnects, and CNT arrays as through-silicon vias (TSV). Reprinted from Ref [26], Copyright 2016, with permission of RSC Publishing.

#### 5. Conclusions

For a vertical CNT-graphene heterostructure, a covalently bonded seamless CNT-graphene junction has been proposed to reduce the electrical contact resistance due to the superior electron transport properties of the two nanocarbons. In principle, a 3D all-carbon heterostructure made up of a CNT array standing on a graphene layer would mitigate the contact resistance problem. In practice, the growth of vertically aligned CNTs on graphene without damaging the latter is a nontrivial task, and even simulating a seamless contact for first-principle calculations to shed some light on transport across the interface remains a challenge. Although the structures studied so far theoretically are limited to small-diameter (for example, (4,4) and (8,0) CNT) SWCNT-graphene heterojunctions, interesting discoveries have been made. For example, a semiconducting (8,0) CNT may be transformed into metallic under certain heterostructure configurations [43, 54]. Most of the CNT-graphene heterostructures have been synthesized by CVD methods, which are usually adapted from the CNT growth recipes with careful control of catalyst deposition and catalyst-substrate interactions. Thus far, the experimental findings, in conjunction with atomistic models used in

theoretical calculations, are still a long way from being conclusive on the interfacial atomic arrangements. Therefore, novel techniques are needed to reveal detailed interfacial information. For example, the ratio of sp²/sp³ bonding can be extracted from the measured density of states, if an atomically clean CNT–graphene junction can be prepared for advanced TEM and STM analyses. Such an approach poses a great challenge in the experimental study of this heterostructure, while overcoming such challenge would yield enormous gain in understanding the electronic transport within the heterostructure. With enhanced understanding, the application potentials of this heterostructure would become more achievable.

**Funding:** Two authors (CZ and JP) acknowledge the financial support of the International Science & Technology Cooperation Program of Guangdong Province (2019A050510011).

**Conflict of Interest:** The authors declare that they have no conflict of interest.

#### References

- [1] S. Kincal, C. M. Abraham, and K. Schuegraf, IEEE Trans. Electron Devices 61, 1914 (2014).

- [2] C. Adelmann, L.G. Wen, A.P. Peter, Y.K. Siew, K. Croes, J. Swerts, M. Popovici, K. Sankaran, G. Pourtois, and S. Van Elshocht, in *Interconnect Technology Conf./Advanced Metallization Conf.* (IITC/AMC) (2014), pp. 173-176.

- [3] K. Sankaran, S. Clima, M. Mees, and G. Pourtois, ECS J. Solid State Sci. Technol. 4, N3127 (2015).

- [4] B. Li, C. Christiansen, D. Badami, and C. Y. Yang, Microelectron. Reliab. 54, 712 (2014).

- [5] Y. Chai, C. P. Chan, Y. Fu, Y. Chuang, and C. Liu, IEEE Electron Device Lett. 29, 1001 (2008).

- [6] K. J. Lee, A. P. Chandrakasan, and J. Kong, IEEE Electron Device Lett. 32, 557 (2011).

- [7] B. Q. Wei, R. Vajtai, and P. M. Ajayan, Appl. Phys. Lett. 79, 1172 (2001).

- [8] C. A. Santini, P. M. Vereecken, A. Volodin, G. Groeseneken, S. De Gendt, and C. V. Haesendonck, Nanotechnol. 22, 395202 (2011).

- [9] A. A. Vyas, C. Zhou, Y. Chai, P. Wang, and C.Y. Yang, Nanotechnol. 27, 375202 (2016).

- [10] R. Murali, K. Brenner, Y. Yang, T. Beck, and J. D. Meindl, IEEE Electron Device Lett. 30, 611 (2009).

- [11] X. Chen, K. J. Lee, D. Akinwande, G. F. Close, S. Yasuda, B. C. Paul, S. Fujita, J. Kong, and H-S. P. Wong, in *IEEE Int. Electron Devices Meeting (IEDM)* (2009), pp. 581–584.

- [12] T. Yu, C. W. Liang, C, Kim, E. S. Song, and B. Yu, IEEE Electron Device Lett. 32, 1110 (2011).

- [13] Q. Ngo, A. M. Cassell, A. J. Austin, J. Li, S. Krishnan, M. Meyyappan, and C. Y. Yang, IEEE Electron Device Lett. 27, 221 (2006).

- [14] J. Coiffic, M. Fayolle, H. Le Poche, S. Maitrejean, and S. Olivier, in *IEEE Int. Interconnect Technology Conf.* (2008), pp. 153–155.

- [15] S. Vollebregt, A. N. Chiaramonti, J. van der Cingel, K. Beenakker, and R. Ishihara, Japan. J. Appl. Phys. 52, 04CB2 (2013).

- [16] C. Zhou, A. A. Vyas, P. Wilhite, P. Wang, M. Chan, and C. Y. Yang, IEEE Electron Device Lett. 36, 71 (2015).

- [17] M. Nihei, A. Kawabata, D. Kondo, M. Horibe, S. Sato, and Y. Awano, Japan. J. Appl. Phys. 44, 1626 (2005).

- [18] A. P. Graham, G. S. Duesberg, W. Hoenlein, F. Kreupl, M. Liebau, R. Martin, B. Rajasekharan, W. Pamler, R. Seidel, W. Steinhoegl, and E. Unger, Appl. Phys. A 80, 1141 (2005).

- [19] Y. Jiang, P. Wang, and L. Li, Nanotechnol. 22, 365704 (2011).

- [20] S. C. Lim, J. H. Jang, D. J. Bae, G. H. Han, S. Lee, I. S. Yeo, and Y. H. Lee, Appl. Phys. Lett. 95, 264103 (2009).

- [21] P. Wilhite, A. A. Vyas, J. Tan, T. Yamada, P. Wang, J. Park, and C. Y. Yang, Semicond. Sci. Technol. 29, 054006 (2014).

- [22] W. Wu, S. Krishnan, T. Yamada, X. Sun, P. Wilhite, R. Wu, K. Li, and C. Y. Yang, Appl. Phys. Lett. 94, 163113 (2009).

- [23] M. H. van der Veen, Y. Barbarin, Y. Kashiwagi, and Z. Tokei, in *Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC) IEEE International* (2014), pp. 181-184.

- [24] Y. Zhu, C. Zhang, G. Casillas, Z. Sun, Z. Yan, G. Ruan, Z. Peng, A. O. Raji, C. Kittrell, R. H. Hauge, and J. M. Tour, Nat. Commun. 3, 1225 (2012).

- [25] R. F. A. Ramos, M. Fayolle, J. Dijon, C. P. Murray, and J. McKenna, in *IEEE Int. Interconnect Technology Conf./Advanced Metallization Conf. (IITC/AMC)* (2016), pp. 48–50.

- [26] K. Ghosh, N. Ranjan, Y. K. Verma, and C. S. Tan, RSC Advances 6, 53054 (2016).

- [27] J. H. Ryu, G. J. Lee, W. S. Kim, H. E. Lim, M. Mativenga, K. C. Park, and H. K. Park, Materials 7, 1975 (2014).

- [28] R. Rao, G. Chen, L. M. Arava, K. Kalaga, M. Ishigami, T. F. Heinz, P. M. Ajayan, and A. R. Harutyunyan, Sci. Rep. 3, 1891 (2013).

- [29] D. H. Lee, J. E. Kim, T. H. Han, J. W. Hwang, S. Jeon, S. Y. Choi, S. H. Hong, W. J. Lee, R. S. Ruoff, and S. Kim, Advanced Materials 22, 1247 (2010).

- [30] Y. S. Kim, K. Kumar, F. T. Fisher, and E. H. Yang, Nanotechnol. 23, 015301 (2012).

- [31] X. Lin, P. Liu, Y. Wei, Q. Li, J. Wang, Y. Wu, C. Feng, L. Zhang, S. Fan, and K. Jiang, Nat. Commun. 4, 2920 (2013).

- [32] S. Engels, P. Weber, B. Terres, J. Dauber, C. Meyer, C. Volk, S. Trellenkamp, U. Wichmann, and C. Stampfer, Nanotechnol. 24, 035204 (2013).

- [33] T. Matsumoto and S. Saito, J. Phys. Soc. Japan 71, 2765 (2002).

- [34] V. T. Dang, D. D. Nguyen, T. T. Cao, P. H. Le, D. L. Tran, N. M. Phan, and V. C. Nguyen, Adv. Nat. Sci.: Nanosci. Nanotechnol. 7, 033002 (2016).

- [35] L. Ping, P. X. Hou, C. Liu, J. Li, Y. Zhao, F. Zhang, C. Ma, K. Tai, H. Cong, and H. M. Cheng, Nanoscale 9, 8213 (2017).

- [36] C. S. Rout, A. Kumar, T. S. Fisher, U. K. Gautam, Y. Bando, and D. Golberg, RSC Adv. 2, 8250 (2012).

- [37] Z. Yan, L. Ma, Y. Zhu, I. Lahiri, M. G. Hahm, Z. Liu, S. Yang, C. Xiang, W. Lu, Z. Peng, Z. Sun, C. Kittrell, J. Lou, W. Choi, P. M. Ajayan, and J. M. Tour, ACS Nano 7, 58 (2013).

- [38] S. S. J. Aravind, V. Eswaraiah, and S. Ramaprabhu, J. Mater. Chem. 21, 15179 (2011).

- [39] J. Jiang, Y. Li, C. Gao, N. D. Kim, X. Fan, G. Wang, Z. Peng, R. H. Hauge, and J. M. Tour, ACS Appl. Mater. Interfaces 8, 7356 (2016).

- [40] R. V. Salvatierra, D. Zakhidov, J. Sha, N. D. Kim, S. K. Lee, A. O. Raji, N. Zhao, and J. M. Tour, ACS Nano 11, 2724 (2017).

- [41] M. Zhao, X. Liu, Q. Zhang, G. Tian, J. Huang, W. Zhu, and F. Wei, ACS Nano 6, 10759 (2012).

- [42] A. Istratov, H. Hieslmair, and E. Weber, Appl. Phys. A 70, 489 (2000).

- [43] W. Du, Z. Ahmed, Q. Wang, C. Yu, Z. Feng, G. Li, M. Zhang, C. Zhou, R. Senegor, and C. Y. Yang, 2D Materials 6, 042005 (2019).

- [44] F. D. Novaes, R. Rurali, and P. Ordejón, ACS Nano 4, 7596 (2010).

- [45] G. K. Dimitrakakis, E. Tylianakis, and G. E. Froudakis, Nano Lett. 8, 3166 (2008).

- [46] The International Technology Roadmap for Semiconductors 2.0 Interconnect. (2015),

- https://www.semiconductors.org/wp-content/uploads/2018/06/6\_2015-ITRS-2.0\_Interconnect.pdf. Accessed 16 July 2020.

- [47] D. Kondo, S. Sato, and Y. Awano, Appl. Phys. Express 1, 074003 (2008).

- [48] V. Jousseaume, J. Cuzzocrea, N. Bernier, and V. T. Renard, Appl. Phys. Lett. 98, 123103 (2011).

- [49] G. Tian, M. Q. Zhao, D. Yu, X. Y. Kong, J. Q. Huang, Q. Zhang, and F. Wei, Small 10, 2251 (2014).

- [50] Y. Xue, Y. Ding, J. Niu, Z. Xia, A. Roy, H. Chen, J. Qu, Z. L. Wang, and L. Dai, Sci. Adv. 1, 2375 (2015).

- [51] C. Zhou, R. Senegor, Z. Baron, Y. Chen, S. Raju, A. A. Vyas, M. Chan, Y. Chai, and C. Y. Yang, Nanotechnol. 28, 054007 (2017).

- [52] R. Senegor and Z. Baron, Carbon Nanotubes on Graphene: Electrical and Interfacial Properties, BSEE thesis (Santa Clara University, 2017), pp. 17-18.

- [53] J. Shaffer and A. Michelmore, Process Optimization for Carbon Nanotubes-on-Graphene Fabrication, BSEE thesis (Santa Clara University, 2018), pp. 7-13.

- [54] Y. Mao and J. Zhong, New J. Phys. 11, 093002 (2009).

- [55] J. Gonzalez, F. Guinea, and J. Herrero, Phys. Rev. B 79, 165434 (2009).

- [56] D. Baowan, B. J. Cox, and J. M. Hill, Carbon 45, 2972 (2007).

- [57] D. Baowan, B. J. Cox, N. Thamwattana, and J. M. Hill, in *IUTAM Symposium on Modelling Nanomaterials and Nanosystems* (2009), pp. 109-121.

- [58] H. W. Kroto, Nature 329, 529 (1987).

- [59] H. Terrones and M. Terrones, New J. Phys. 5, 126 (2003).

- [60] T. W. Ebbesen and T. Takada, Carbon 33, 973 (1995).

- [61] N. Yang, D. Yang, L. Chen, D. Liu, M. Cai, and X. Fan, Materials 10, 1300 (2017).

- [62] M. F. Budyka, T. S. Zyubina, A. G. Ryabenko, S. H. Lin, and A. M. Mebel, Chemical Physics Lett. 407, 266 (2005).